神戸大学情報知能工学科の難関・論理回路についてです。せっかく勉強したので、自分のためにもまとめときます。

第一章は特にないからとばす。

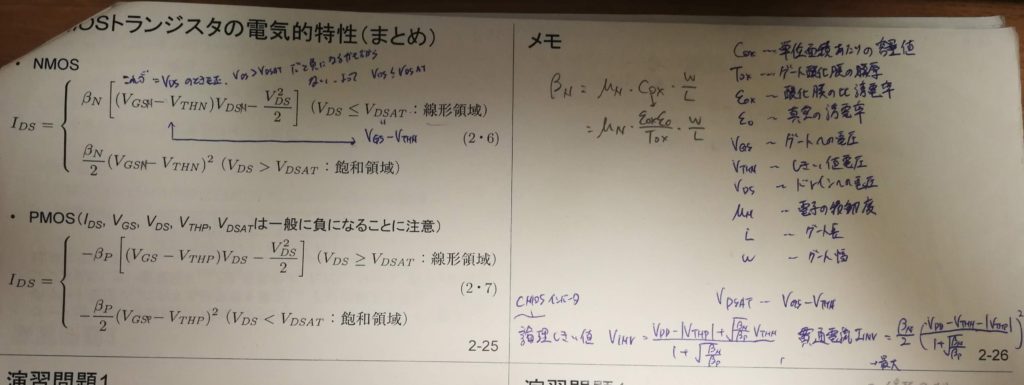

第二章

とりあえずこの式を覚えときゃおk。このわけわからんVの順番は

{Vgs(ガソリンスタンドで)-Vthn(ち○こ)}Vds(だす)

と覚えました。

三章も飛ばします。

第四章

ブール代数は使わなかった。

トランジスタレベルの構成は必ずPMOSが上で、PMOSとNMOSで並列・直列が必ず異なる。

PMOSが並列(つまりNMOSが直列)ならばNANDだし、PMOSが直列(NMOSが並列)ならNORになることをちゃんと覚えて、どっちがどっちだっけ?とならないように。教科書P46

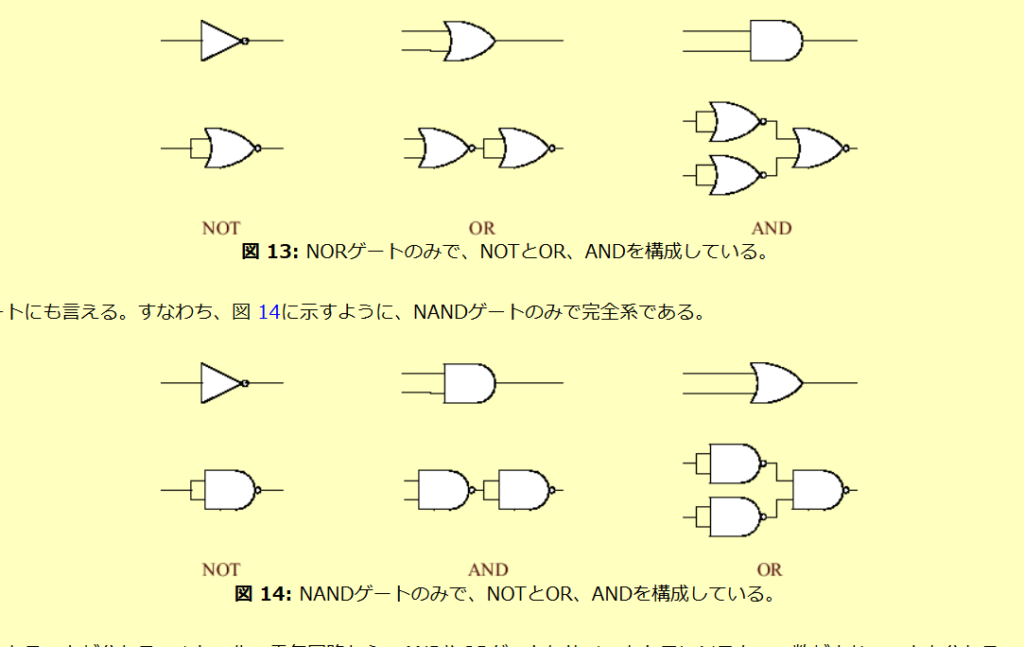

・完全形

NAND,NORは完全形です。つまり、それ一つでANDだろうがXORだろうが設計することができるということ。

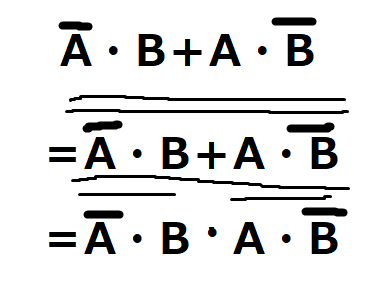

また、次の論理式をNORのみで設計せよ、という問題はバーを2つつけてみると(ド・モルガンの定理よりもとの式と同値)大体いい感じになる。

・CMOS複合ゲート

AOI複合ゲートは(OAIも)全体にバーがつく。まず、AとBはANDだからPMOSが並列になり、NMOSが直列になる。Cは(パーツで考えたら)孤立しているから、とりあえずNMOSとPMOSを用意しておく。(A*B)とCはORでつながっているから、PMOS側は直列に、NMOS側は並列にそれぞれつなぐ。YはPMOSとNMOSのあいだから出てきます。一度理解すれば簡単です。教科書P51

XORをNANDゲートのみで設計するのは覚えたほうが早そう。僕は自力でできなかった。

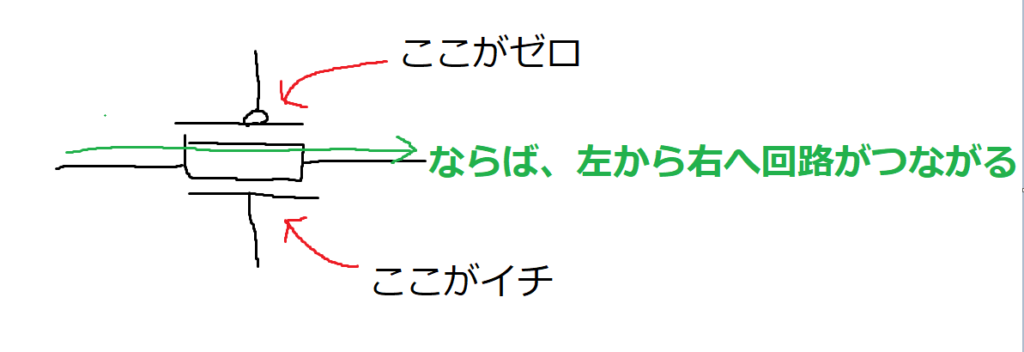

・CMOSトランスミッションゲート

CMOSトランスミッションゲートは一見難しそうだが、理解すれば設計できるようになります。

CMOSトランスミッションゲートを設計する問題は基本的に2入力なので、全部のパターンがうまくいくように繋げれば解けます。P57 のXORゲートの例やP76のマルチプレクサとにらめっこしましょう。

第五章

プロセスフローはテストに出ないし僕もわからんので飛ばします。

レイアウトは最初まじでわからないし、テストが近づいてもわからないですが見方をつかめば理解は速いです。

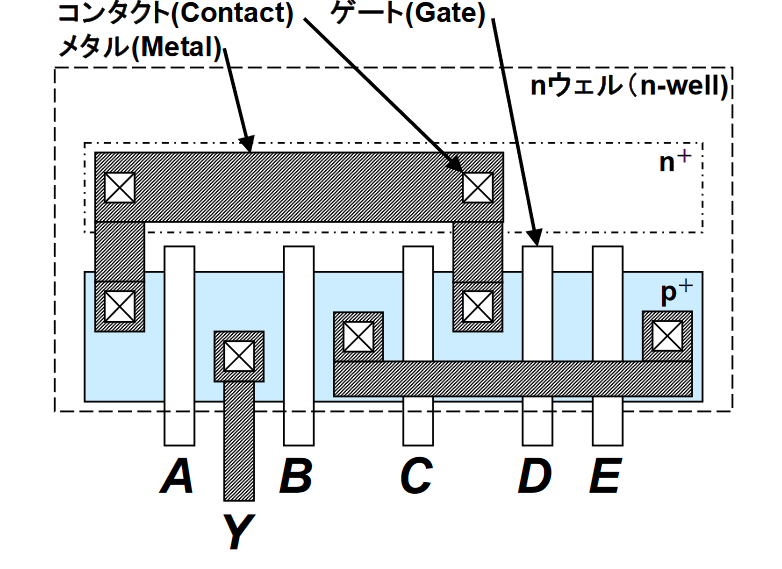

前述のように、PMOSは上、NMOSは下にかかれていて、それぞれ直列/並列は逆転関係です。なので回路を知るには上半分だけ理解できればおk。実際テストでも上半分しか描かれていないです。

レイアウトの見方はABCDEを細長い”かまぼこ”と見てください。その”かまぼこ”が一つのMOSとなっています。

この問題を例に取ると、p+拡散領域の上にMOSができているのでこれはPMOSです。

そして電源とつながっているのがAとC、DつまりA,C,Dはそれぞれ直接つながっています。また、B,CとEも直接つながっています。

あとはこねくって並列と直列を作れば論理式ができます。最後に全体にバーをつけるのを忘れずに。

第六章

デコーダ、エンコーダ、プライオリティエンコーダ、マルチプレクサ、デマルチプレクサの5つの名前と対応する真理値表を覚えましょう。

真理値表から設計するのはやれば理解できるはずです。

第七章

・Dラッチ

G=1のときDのまね、G=0のとき継続

・Dフリップフロップ

CLKの立ち上がり時のDを継続

この文章をグラフで言わんとしていることはわかるはず。

第八章

むずいからわからん